Hello, I am designing a MOSFET-based switch to power the analog part of my circuit only when needed in order to save some power and extend the battery life. I am not an EE so I apologise if my questions are a bit naive...

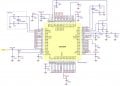

My (rather limited) understanding of MOSFET is that they should not require a gate resistor however I read here SE thread that it could a good idea to prevent ringing. In the same thread they also mention a high impedance resistor to ground. The schematics would therefore look like this (AEN is one of the digital outputs of my microcontroller and A0 is an analog input, there are separate analog and digital power rails):

Q1 Did I pick the right MOSFET ?

I selected a DMN2005LP4K-7 (datasheet) for the following reasons:

Q2 Do I really need R1 and R2 ?

AEN will be forced down by the microcontroller so do I really need the pull down resistor R2? As for R1...

Thanks a lot !

My (rather limited) understanding of MOSFET is that they should not require a gate resistor however I read here SE thread that it could a good idea to prevent ringing. In the same thread they also mention a high impedance resistor to ground. The schematics would therefore look like this (AEN is one of the digital outputs of my microcontroller and A0 is an analog input, there are separate analog and digital power rails):

Q1 Did I pick the right MOSFET ?

I selected a DMN2005LP4K-7 (datasheet) for the following reasons:

- Rds(on) is very low (400mOhm @2.7V) and my main goal is precisely to save power.

- The gate threshold voltage is very low (0.5-0.9V) so it should be full on with a logic high of 2.8V.

- VDD=VDDA=2.8V so with Vds=20V and Vgs=10V I am on the safe side

- The total resistance (FSR + R3) is so high that I shouldn't have more than 1mA going through so a max drain current of 300mA is plenty and for the same reason 400mW of power dissipation is way more than I will ever need.

Q2 Do I really need R1 and R2 ?

AEN will be forced down by the microcontroller so do I really need the pull down resistor R2? As for R1...

Thanks a lot !

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin

.

.