I need to use a high-capacity mass storage device (SSD, NVMe) with an FPGA (I'm using Trion from Efinix). Since I think it's very difficult to use SATA/PCIe interfaces natively with these FPGAs, I was thinking of implementing a USB host and then using an external USB<->SATA or USB<->NVMe bridge to take advantage of the external drive (speed isn't important at this stage).

I imagine a good USB host to connect to the FPGA would be the MAX3421E (are there alternatives?), which can be controlled via SPI.

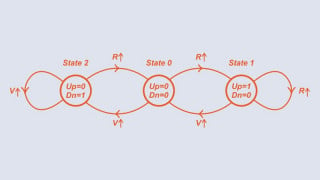

But now I'm wondering, once the MAX3421 is connected to the SPI bus, how can I control it from the FPGA? If I want to write/read RAW data from the USB Mass Storage device (without considering any file systems), how complex is it to build a system on the FPGA (VHDL/Verilog) that can do this?

I don't think it's enough to just tell the SPI bus "read a byte at sector/address" or "write this byte to sector/address."

Are there any pre-built IPs that can help me?

Do you have any general suggestions?

I imagine a good USB host to connect to the FPGA would be the MAX3421E (are there alternatives?), which can be controlled via SPI.

But now I'm wondering, once the MAX3421 is connected to the SPI bus, how can I control it from the FPGA? If I want to write/read RAW data from the USB Mass Storage device (without considering any file systems), how complex is it to build a system on the FPGA (VHDL/Verilog) that can do this?

I don't think it's enough to just tell the SPI bus "read a byte at sector/address" or "write this byte to sector/address."

Are there any pre-built IPs that can help me?

Do you have any general suggestions?

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin