Hi all, I've bought a couple of 74LS593 register/counters to make a Program Counter for my breadboard CPU. I'm having trouble interpreting the datasheets for this chip. I've found these sheets:

The timing diagram on page 5 of the second sheet is very confusing, especially the register load section. The first sheet has a truth table on page 2 which makes more sense. However, two separate rows say:

Anyway, what I want is three control lines:

Cheers, Warren

The timing diagram on page 5 of the second sheet is very confusing, especially the register load section. The first sheet has a truth table on page 2 which makes more sense. However, two separate rows say:

- Data of Q bus is loaded into the counter

- Data of Q bus is stored in the register

Anyway, what I want is three control lines:

- Enable the output on the Q-bus, or set it to high impedance (place the PC on the data bus or not)

- Load the register with the Q bus value (load the PC for jump and branch instructions)

- Increment the counter value (increment the PC)

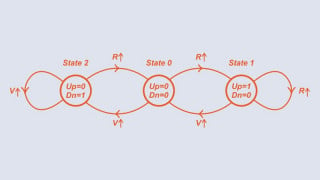

- RCO# from the low counter connects to CCKEN# of the high counter as the cascade (# means active low)

- The main CPU clock signal is connected to both RCLK and CCLK

- G# is always low. Setting G low means high-impedance output. Setting G high outputs the PC value on the address bus.

- Use CCKEN as the control line to increment the counter value

- Use RCKEN# (active low) as the control line to load the register

- CCLR# is tied high

Cheers, Warren

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin