So I was taking sample readings with a logic analyzer to get an understanding why specific parts were used in a particular piece of equipment.

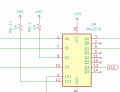

One of these readings I took was where the 1MHz system clock passes through a 54LS375 latch (see attachment - pins 15 and 13). The CLK line continues to a display controller IC on another board.

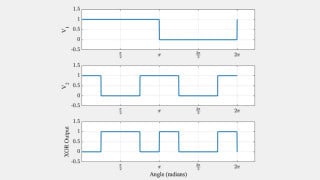

The only discernible difference in the waveform on both ends was that because of propagation delays, the duty cycle of the inbound clock signal was 43% while the duty cycle of the outgoing CLK signal was a perfect 50%.

So how critical is duty cycle in the main system clock?

Obviously you don't want the duty cycle to be all the way down to 10% or as high as 90%, but is there some kind of leeway?

Or do I need to make sure that everything that uses the main clock has a perfect 50% duty cycle at its clock pin?

One of these readings I took was where the 1MHz system clock passes through a 54LS375 latch (see attachment - pins 15 and 13). The CLK line continues to a display controller IC on another board.

The only discernible difference in the waveform on both ends was that because of propagation delays, the duty cycle of the inbound clock signal was 43% while the duty cycle of the outgoing CLK signal was a perfect 50%.

So how critical is duty cycle in the main system clock?

Obviously you don't want the duty cycle to be all the way down to 10% or as high as 90%, but is there some kind of leeway?

Or do I need to make sure that everything that uses the main clock has a perfect 50% duty cycle at its clock pin?

Attachments

-

61.2 KB Views: 20

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin