Hi, is there anyone who can help me/guide me to solve the problem? Even if you could recommend me any teacher, senior, book, or paper, it would be of great help to me. I have come up with a dummy solution, but I am pretty sure it's not that accurate (I can show you my answer). I really appreciate guidance in any form. Thanks for taking the time to read this post!

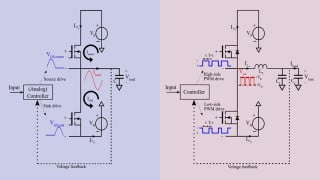

Suppose there is a piezoelectric crystal 4um * 4 um, thickness 500 nm, with dielectric constant of 10. There are metal electrodes at the top and bottom of the crystal. Suppose ultrasonic waves are applied at a frequency of 1 GHz and ac voltage with peak of 0.3 V is generated across the electrodes. Now suppose a diode and capacitor is connected to the electrodes to create a halfwave rectifier and voltage smoothing circuit.

i> Design (materials, structure, doping etc) the diode and capacitor to obtain best rectification/smoothing, lowering peak-to-peak ripples with the constraints that the area of diode and capacitor should be less than 4um by 4um and thickness less than 500nm.

ii> Design the layout of the circuit (how fabricated structure will look) with the on-chip piezoelectric

iii>Extract the equivalent capacitance across the metal electrodes of the piezoelectric crystal considering all parasitic capacitances. Show all parasitic capacitances in the diagram.

Suppose there is a piezoelectric crystal 4um * 4 um, thickness 500 nm, with dielectric constant of 10. There are metal electrodes at the top and bottom of the crystal. Suppose ultrasonic waves are applied at a frequency of 1 GHz and ac voltage with peak of 0.3 V is generated across the electrodes. Now suppose a diode and capacitor is connected to the electrodes to create a halfwave rectifier and voltage smoothing circuit.

i> Design (materials, structure, doping etc) the diode and capacitor to obtain best rectification/smoothing, lowering peak-to-peak ripples with the constraints that the area of diode and capacitor should be less than 4um by 4um and thickness less than 500nm.

ii> Design the layout of the circuit (how fabricated structure will look) with the on-chip piezoelectric

iii>Extract the equivalent capacitance across the metal electrodes of the piezoelectric crystal considering all parasitic capacitances. Show all parasitic capacitances in the diagram.

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin