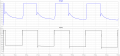

I am currently simulating this circuit below, however, i am running into a problem whenever the signal goes through the gate driver it comes out somewhat deformed. I already tried adjusting the bootstrap capacitor but that didnt help. only thing i can think of is maybe the dead time value being inadequate.

Attachments

-

48.3 KB Views: 4

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin