I have a pretty basic question about half bridge motor controller design...

I am working on a half bridge controller that I want to drive fairly high currents, so will require the use of multiple high side and low side power FETs.

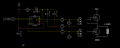

My design is so far based on the NCP5183 High side bootstrap and Low side driver IC.

My circuit design uses 3 of these ICs each driving a single high and low side power FET pair, with the power FETS driving the the motor in parallel.

If I run the circuit so that only a single NCP5183 and power FET pair is driving the motor driver then the system works perfectly.

However when I try and get these 3 circuits driving together the high side power FETs stop switching correctly. The waveform of the high side power FETs becomes very erratic.

After spending a lot of time researching this I have come to the conclusion that the normal way to design a half bridge is to have a single driver circuit, and to drive multiple power FETS gates at once (with the gates connected together). However as described my circuit has multiple driver circuits driving single pairs of FETS.

So my question is, firstly am I correct in thinking that my design is flawed, and secondly what causes the system to stop operating properly when designed like I have?

I am working on a half bridge controller that I want to drive fairly high currents, so will require the use of multiple high side and low side power FETs.

My design is so far based on the NCP5183 High side bootstrap and Low side driver IC.

My circuit design uses 3 of these ICs each driving a single high and low side power FET pair, with the power FETS driving the the motor in parallel.

If I run the circuit so that only a single NCP5183 and power FET pair is driving the motor driver then the system works perfectly.

However when I try and get these 3 circuits driving together the high side power FETs stop switching correctly. The waveform of the high side power FETs becomes very erratic.

After spending a lot of time researching this I have come to the conclusion that the normal way to design a half bridge is to have a single driver circuit, and to drive multiple power FETS gates at once (with the gates connected together). However as described my circuit has multiple driver circuits driving single pairs of FETS.

So my question is, firstly am I correct in thinking that my design is flawed, and secondly what causes the system to stop operating properly when designed like I have?

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin