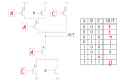

The exercise from "Introduction to computer systems" textbook. At first, I figured out this arrangement:

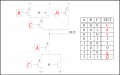

But in the case of A=1, B=1, and C= 0 →

It short circuited to the ground. So then i figured out following arrangement:

But in the case of A=1, B=0, C=1 there isn't way to the ground since lower B gates open. Is it okay or this is also faulty case and i should always provide the pass to the ground in the zero out case?

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin