Hello, please help.

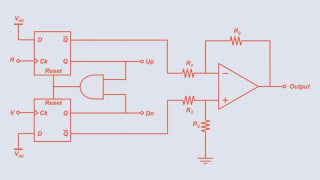

For my electronic design, I am experimenting what device will be better, FPGA or CPLD, I wish to compile and determine the amount of space this takes on a device then judge my needs. I am trying to do as per this image, I have simple task of finding right 3 byte condition in parallel data stream, coming at about 12-22 Mhz, lets say I will have about 50-100 of these 3 byte conditions. These 50-100 or so conditons will in turn, signal 20 or so different type events ( pins). So some event pins will work for a multitude of 3 byte conditions.

Can anybody code for me a simple example? I am mostly self taught C programmer, please understand my difficulty.

For example: combination 144,136,88 ( 0x009000800058) activates a pin, combination 0,196,0 (0x000000C40000) activates another pin.

As per the Drawing, thank you.

For my electronic design, I am experimenting what device will be better, FPGA or CPLD, I wish to compile and determine the amount of space this takes on a device then judge my needs. I am trying to do as per this image, I have simple task of finding right 3 byte condition in parallel data stream, coming at about 12-22 Mhz, lets say I will have about 50-100 of these 3 byte conditions. These 50-100 or so conditons will in turn, signal 20 or so different type events ( pins). So some event pins will work for a multitude of 3 byte conditions.

Can anybody code for me a simple example? I am mostly self taught C programmer, please understand my difficulty.

For example: combination 144,136,88 ( 0x009000800058) activates a pin, combination 0,196,0 (0x000000C40000) activates another pin.

As per the Drawing, thank you.

Attachments

-

167.3 KB Views: 6

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin