Hi,

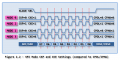

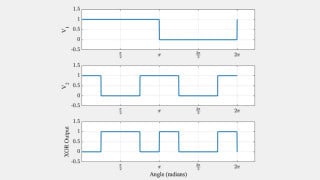

I've been trying to program a PIC with the correct CLK timings to achieve this shape: (See READ-WRITE)

I've posted 2x examples from a data analyser.

1/BYTES in sequence with correct? timing.

2/The Clock polarity is set to IDLE LOW (as READ WRITE) but it starts way in front of the BYTE READing section. Does this matter?

Camerart.

I've been trying to program a PIC with the correct CLK timings to achieve this shape: (See READ-WRITE)

I've posted 2x examples from a data analyser.

1/BYTES in sequence with correct? timing.

2/The Clock polarity is set to IDLE LOW (as READ WRITE) but it starts way in front of the BYTE READing section. Does this matter?

Camerart.

Attachments

-

279.2 KB Views: 8

-

189.9 KB Views: 10

-

144.1 KB Views: 8

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin