Hello,

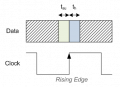

I've came accross the terms 'asynchronous' and 'synchronous' protocols, and I'm trying to understand their meanings in this context. I've noticed that UART is considered an asynchronous protocol, while SPI is synchronous. It appears to be linked to data transmission timing.

Could someone help me to understand what is meant by 'asynchronous' and 'synchronous' when referring to communication protocols?

I've came accross the terms 'asynchronous' and 'synchronous' protocols, and I'm trying to understand their meanings in this context. I've noticed that UART is considered an asynchronous protocol, while SPI is synchronous. It appears to be linked to data transmission timing.

Could someone help me to understand what is meant by 'asynchronous' and 'synchronous' when referring to communication protocols?

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin