Here is my task.

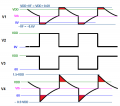

For astable multivibrator circuit find analytical expressions and sketch timing diagrams for voltages v1, v2, v3 and v4. It is known: R1, R2, C, Vdd, Vd (voltage drop on forward biased diodes) and Vthreshold (threshold voltage for CMOS circuit). CMOS inverters have protection diodes on input.

Here are my thoughts:

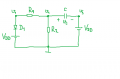

Let's sat at beginning that v2 = Vdd. It must be then v3 = 0. Equivalent circuit for this case is:

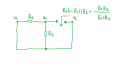

It is equivalent to this:

It is simple series RC circuit. It is easy to find solution for it (I wrote direct solution, I didn't show steps because it is not necessary).

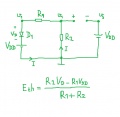

Expression is valid till v1 goes to Vthreshold. It will occur at some T1. After solving equation v1(T=t1) = Vthreshold, we get T1=R2*C*ln(Vdd/(Vdd-Vthreshold)) = R2*C*ln2.

When v1 goes to Vthreshold, v2 will be low (= 0V) because v1 is high. v3 will be high in that case (= VDD). I stucked there. I don't know what to do next. Any idea?

For astable multivibrator circuit find analytical expressions and sketch timing diagrams for voltages v1, v2, v3 and v4. It is known: R1, R2, C, Vdd, Vd (voltage drop on forward biased diodes) and Vthreshold (threshold voltage for CMOS circuit). CMOS inverters have protection diodes on input.

Here are my thoughts:

Let's sat at beginning that v2 = Vdd. It must be then v3 = 0. Equivalent circuit for this case is:

It is equivalent to this:

It is simple series RC circuit. It is easy to find solution for it (I wrote direct solution, I didn't show steps because it is not necessary).

Expression is valid till v1 goes to Vthreshold. It will occur at some T1. After solving equation v1(T=t1) = Vthreshold, we get T1=R2*C*ln(Vdd/(Vdd-Vthreshold)) = R2*C*ln2.

When v1 goes to Vthreshold, v2 will be low (= 0V) because v1 is high. v3 will be high in that case (= VDD). I stucked there. I don't know what to do next. Any idea?