Hi, I'm working on a textbook question that is giving me some trouble:

A given ALU can perform 16 unique operations. Describe the multiplexer circuit needed to select exactly one of the 16 operations.

I'm not sure what they mean by "operation" other than an operator doing work on a set of operands. Since they don't give the actual operations (ADD, SUBTRACT, etc.) or the bit length, is it reasonable to represent the entire operation as a single bit?

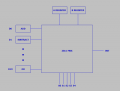

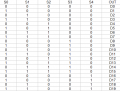

For example, I worked out the truth table and circuit diagram for a 16x1 Multiplexer with a bit length of 1. Obviously an ALU isn't sending 1 bit at a time unless there is sequential timing occurring upstream.. Does this mean a block diagram of a traditional MUX is more appropriate? I like my schematic below because it shows the actual transformation but I fear I haven't adequately answered the question. Thanks for the help!

A given ALU can perform 16 unique operations. Describe the multiplexer circuit needed to select exactly one of the 16 operations.

I'm not sure what they mean by "operation" other than an operator doing work on a set of operands. Since they don't give the actual operations (ADD, SUBTRACT, etc.) or the bit length, is it reasonable to represent the entire operation as a single bit?

For example, I worked out the truth table and circuit diagram for a 16x1 Multiplexer with a bit length of 1. Obviously an ALU isn't sending 1 bit at a time unless there is sequential timing occurring upstream.. Does this mean a block diagram of a traditional MUX is more appropriate? I like my schematic below because it shows the actual transformation but I fear I haven't adequately answered the question. Thanks for the help!

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin