3.3v to 5v pulse inverter current spikes question

- Thread starter yef smith

- Start date

Scroll to continue with content

Bordodynov

- Joined May 20, 2015

- 3,430

That is called cross-conduction, or shoot-through. It happens when one FET turns on before the other FET is completely turned off. The solution is timing circuits in the gate signals to assure that the "on's" arrive after the "off's". Often this is done with 1 diode, one R, and one C per gate.

Sometimes it is done with just a diode and resistor, relying on the gate capacitance as the delay element. This is risky because that capacitance is not tightly controlled, and can change significantly from one manufacturer to another, one lot to another, and even one device to another in the same lot.

ak

Sometimes it is done with just a diode and resistor, relying on the gate capacitance as the delay element. This is risky because that capacitance is not tightly controlled, and can change significantly from one manufacturer to another, one lot to another, and even one device to another in the same lot.

ak

Last edited:

Hello Eric , could you give intuition regarding why it’s crating a time gap between the opening of the mosfets ?

I understand that the voltages at the gate is charges with gate charge capacitance .

So by changing this rate the Vg Charges at different rate.

If I got the logic correctly , how the diode structure makes this effect ?

Thanks .

I understand that the voltages at the gate is charges with gate charge capacitance .

So by changing this rate the Vg Charges at different rate.

If I got the logic correctly , how the diode structure makes this effect ?

Thanks .

Hi yef,

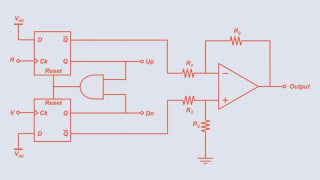

As others have noted, you need a little non drive period [dead time] between the MOSFETs switching On/Off/On/Off......

With the drive voltage changing state with a rise/fall time of 30nSec, and adding the off response time of the MOSFET, both MOSFET's are On at the overlap time, hence a large current spike.

The BAT diodes slightly delay the MOSFET at the switch ON edge, so creating a short dead time space.

The inter electrode capacitance of the parallel BAT introduces a further small delay.

E

As others have noted, you need a little non drive period [dead time] between the MOSFETs switching On/Off/On/Off......

With the drive voltage changing state with a rise/fall time of 30nSec, and adding the off response time of the MOSFET, both MOSFET's are On at the overlap time, hence a large current spike.

The BAT diodes slightly delay the MOSFET at the switch ON edge, so creating a short dead time space.

The inter electrode capacitance of the parallel BAT introduces a further small delay.

E

Attachments

-

1.9 KB Views: 3

Last edited:

ronsimpson

- Joined Oct 7, 2019

- 4,647

One of the problems is that the input signal goes from 0v to 3.3v with a 5.0v supply. This leaves the top FET with 1.7V Gate-Source. The top FET is almost on.

Hello ,two questions:

1.the solution that was proposed has -6A spike is that ok?

is that ok?

2.I got 440mA and 8W as shown below however bss84 can handle 0.36V.

Is there alternative mosfets i could use?

Thanks.

https://www.onsemi.com/download/data-sheet/pdf/bss84-d.pdf

1.the solution that was proposed has -6A spike

2.I got 440mA and 8W as shown below however bss84 can handle 0.36V.

Is there alternative mosfets i could use?

Thanks.

https://www.onsemi.com/download/data-sheet/pdf/bss84-d.pdf

Last edited:

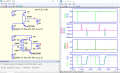

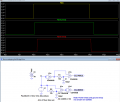

Below is the LTspice sim of circuit that uses one CD4093 quad, Schmidt-trigger NAND gate package to generate the non-overlap function, instead of diodes.

The advantage is, it doesn't slow down the MOSFET turn-on rise-time as an RC delay at the MOSFET gate does.

The non-overlap time is determined by the RC delay (here about 0.9µs).

See how the P-MOSFET gate signal turns off (green trace) before the N-MOSFET gate signal turns on (red trace), and the N-MOSFET turns off before the P-MOSFET turns on.

Note that a level shifter is needed to convert the 3.3V micro signal to the 5V signal for the circuit (the same as needed for the other proposed circuits driving a 5V powered P-MOSFET).

The advantage is, it doesn't slow down the MOSFET turn-on rise-time as an RC delay at the MOSFET gate does.

The non-overlap time is determined by the RC delay (here about 0.9µs).

See how the P-MOSFET gate signal turns off (green trace) before the N-MOSFET gate signal turns on (red trace), and the N-MOSFET turns off before the P-MOSFET turns on.

Note that a level shifter is needed to convert the 3.3V micro signal to the 5V signal for the circuit (the same as needed for the other proposed circuits driving a 5V powered P-MOSFET).

Last edited:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin