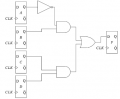

Lets say we have this circuit:

(https://imgur.com/XzkEG90)

tpd(AND)=5 ns, tpd(OR)=5ns, tpd(NOT)=3ns, and tcd of all gates =1ns

FlipFlops: tpcq=1ns, tccq=1ns, tsetup=1ns thold=1ns

First I want to check this circuit for hold-time violations. And then I want to calculate the latency.

What exactly is tccq and tpcq of FlipFlops? I understand that tcd+tccp > thold for the hold-time to be not violated. First I would look for the shortest path. This would be from the FF "D" to the FF "F". The tccq of which FF (D or F or both?) do I have to take in consideration?

(https://imgur.com/XzkEG90)

tpd(AND)=5 ns, tpd(OR)=5ns, tpd(NOT)=3ns, and tcd of all gates =1ns

FlipFlops: tpcq=1ns, tccq=1ns, tsetup=1ns thold=1ns

First I want to check this circuit for hold-time violations. And then I want to calculate the latency.

What exactly is tccq and tpcq of FlipFlops? I understand that tcd+tccp > thold for the hold-time to be not violated. First I would look for the shortest path. This would be from the FF "D" to the FF "F". The tccq of which FF (D or F or both?) do I have to take in consideration?

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin