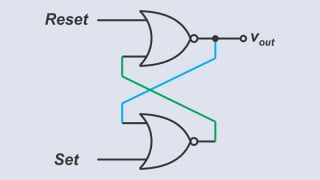

Hello , I am trying to simulate time domain reflectometry and recognise threw the pulse responce if the load is capacitative or inductive.

As you can see its not working .

Where did I go wrong with the concept.

what is the proper way to see threw the time responce if the load is capacitative or inductive?

Thanks.

As you can see its not working .

Where did I go wrong with the concept.

what is the proper way to see threw the time responce if the load is capacitative or inductive?

Thanks.

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin