Hello everyone!

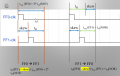

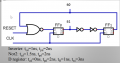

For the following circuit, I need to write the timing constraints of Tclk & Thold, for routes FF0->FF1 & FF1->FF0.

It's given that the clock pulse arrives to FF1 in a delay of 1ns after arriving to FF0.

That's very confusing me, I know how to write the inequalities for Tclk & Thold without clock skew, but once it's added I'm kind of lost.

Without Skew:

FF0->FF1:

Tclk>=Tpcq(FF0)+2*Tpd(NOT)+Tsetup(FF1)

Thold<=Tccq(FF0)+2*Tcd(NOT)

FF1->FF0:

Tclk>=Tpcq(FF1)+Tpd(NOR)+Tsetup(FF1)

Thold<=Tccq(FF0)+Tcd(NOR)

I need your explanation please for how do I add the clock skew to this inequalities and why.

thank you in advance!

For the following circuit, I need to write the timing constraints of Tclk & Thold, for routes FF0->FF1 & FF1->FF0.

It's given that the clock pulse arrives to FF1 in a delay of 1ns after arriving to FF0.

That's very confusing me, I know how to write the inequalities for Tclk & Thold without clock skew, but once it's added I'm kind of lost.

Without Skew:

FF0->FF1:

Tclk>=Tpcq(FF0)+2*Tpd(NOT)+Tsetup(FF1)

Thold<=Tccq(FF0)+2*Tcd(NOT)

FF1->FF0:

Tclk>=Tpcq(FF1)+Tpd(NOR)+Tsetup(FF1)

Thold<=Tccq(FF0)+Tcd(NOR)

I need your explanation please for how do I add the clock skew to this inequalities and why.

thank you in advance!

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin