Hello,There is a demand for a delivery of 3 A through several layers using vias for 17.5 micro seconds.

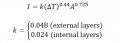

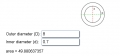

Presented below in the picture is my PCB manufacturer's abilities regarding vias.

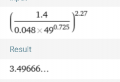

A single via can withstand 1.4 A at shown bellow.

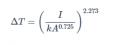

Is there some method to know what temperature rise i will get after 17.5 microseconds at 3A for such VIA?

Thanks.

Presented below in the picture is my PCB manufacturer's abilities regarding vias.

A single via can withstand 1.4 A at shown bellow.

Is there some method to know what temperature rise i will get after 17.5 microseconds at 3A for such VIA?

Thanks.

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin