Hello,In the datasheet shown below they say that the output resistance could be controlled using the COMP pin.

I have tried to simulate this component in LTSPICE.

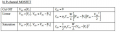

However I cannot understand the datasheet regarding how exactly do I need to use the COMP pin for tuning the output voltage?

LTSPICE file is attached.

Thanks.

https://www.analog.com/media/en/technical-documentation/data-sheets/1261lfa.pdf

I have tried to simulate this component in LTSPICE.

However I cannot understand the datasheet regarding how exactly do I need to use the COMP pin for tuning the output voltage?

LTSPICE file is attached.

Thanks.

https://www.analog.com/media/en/technical-documentation/data-sheets/1261lfa.pdf

Attachments

-

980 bytes Views: 1

Last edited by a moderator: