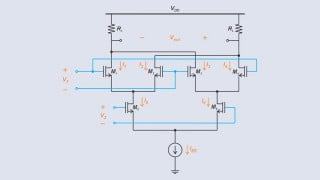

1. I have to read Current transformer reading. CT has both +ve & -ve peaks so I have level shifted the value to 2.5V. As in attached circuit.

2. CT has 50Hz waveform & below is my algo.

3. Attached is my circuit.

4. Problem is there is noise in reading. For same input value i.e CT output, microcontroller reading shows huge variation.

However if I try by connecting external potentiometer reading is stable. So I think no problem on MCU side.

5. Problem is on external circuit. How to remove noise there , can I connect filter capacitor across ac signal??

Cannot add opamp since circuit is cost sensitive.

2. CT has 50Hz waveform & below is my algo.

Code:

1. Init adc

2. Init timer

3. start timer for 1ms

4. take adc reading & store result in array

5. wait while timer set in step 3 expired

6. repeat step 3 to 5 , 20 times for 50Hz

7. in array check for highest reading. This is the peak reading4. Problem is there is noise in reading. For same input value i.e CT output, microcontroller reading shows huge variation.

However if I try by connecting external potentiometer reading is stable. So I think no problem on MCU side.

5. Problem is on external circuit. How to remove noise there , can I connect filter capacitor across ac signal??

Cannot add opamp since circuit is cost sensitive.

Attachments

-

29.6 KB Views: 44

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin