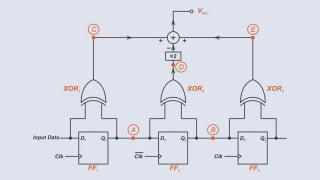

Problem set is in the attached picture.

My working is as such:

This is a CMOS OR AND INVERT (OAI) gate. Traditionally, this has 4 transistors for 2 input. From what I read from text, you would need 2^n transistors (PMOS+NMOS), where n is number of inputs.

The logic expression is as follows: Z=[(B+C)A]'

So for 2 input NOR and AND logic gate, you would need 4+4=8.

Inverter/Nand require 2 transistors (PMOS+NMOS). Which would make the total 10 transistors.

How do you get 6 as the answer? Does the question mean 6 set of transistors? Or does it involve open-drain/collector NMOS where the PMOS is removed and pull up resistor attached to it?

I have trouble understanding the concept. The answer is 6 minimum transistors

My working is as such:

This is a CMOS OR AND INVERT (OAI) gate. Traditionally, this has 4 transistors for 2 input. From what I read from text, you would need 2^n transistors (PMOS+NMOS), where n is number of inputs.

The logic expression is as follows: Z=[(B+C)A]'

So for 2 input NOR and AND logic gate, you would need 4+4=8.

Inverter/Nand require 2 transistors (PMOS+NMOS). Which would make the total 10 transistors.

How do you get 6 as the answer? Does the question mean 6 set of transistors? Or does it involve open-drain/collector NMOS where the PMOS is removed and pull up resistor attached to it?

I have trouble understanding the concept. The answer is 6 minimum transistors

Attachments

-

246.7 KB Views: 9

Last edited:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin