Hello AAC folks,

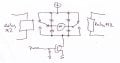

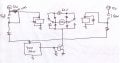

I've designed this h-bridge circuit to run a 60v brushed shunt motor that is controlled by 12v stop-start circuitry, the relay logic prevents catastrophic shoot through (forward and reverse conditions simultaneously)

The tl494 is driving the two n-fets with a 10KHz pwm square wave.

The tip31c's pull down on their collector dividers to apply approximately 10v to the p-fet gates with respect to the source (60v).

The bd136's drive the gate of their respective n-fet, when on, the n-fet gates sit at 0.6v

When running "forwards" (push button FS "forward start" is pressed) , FI2 NO closes turning on the upper tip31c and brings fet F1 Vgs to 10v, turning it on fully.

The lower bd136's gate is brought up to 12v, the transistor turns off and brings fet F2 Vgs to somewhere between 1-10v (depending on the pwm duty cycle), this is all good, the motor runs with adjustable speed. The problem is that the other p-fet R1 gets instantly hot even though its gate stays at 60v (Vgs = 0) in this condition, when inadequately heat-sinked , the fet burns up and shorts out after 5-8 seconds. (F1 and F2 do not get hot)

The same condition happens when going in reverse, this time p-fet F1 burns up

Does anyone know what is happening here?

Thanks!

(PR-1 and 2 NO contacts are a power relay that is energized in both direction conditions, consider it always closed or not there for this)

I've designed this h-bridge circuit to run a 60v brushed shunt motor that is controlled by 12v stop-start circuitry, the relay logic prevents catastrophic shoot through (forward and reverse conditions simultaneously)

The tl494 is driving the two n-fets with a 10KHz pwm square wave.

The tip31c's pull down on their collector dividers to apply approximately 10v to the p-fet gates with respect to the source (60v).

The bd136's drive the gate of their respective n-fet, when on, the n-fet gates sit at 0.6v

When running "forwards" (push button FS "forward start" is pressed) , FI2 NO closes turning on the upper tip31c and brings fet F1 Vgs to 10v, turning it on fully.

The lower bd136's gate is brought up to 12v, the transistor turns off and brings fet F2 Vgs to somewhere between 1-10v (depending on the pwm duty cycle), this is all good, the motor runs with adjustable speed. The problem is that the other p-fet R1 gets instantly hot even though its gate stays at 60v (Vgs = 0) in this condition, when inadequately heat-sinked , the fet burns up and shorts out after 5-8 seconds. (F1 and F2 do not get hot)

The same condition happens when going in reverse, this time p-fet F1 burns up

Does anyone know what is happening here?

Thanks!

(PR-1 and 2 NO contacts are a power relay that is energized in both direction conditions, consider it always closed or not there for this)

Attachments

-

237.2 KB Views: 44

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin