johnson counter

- Thread starter dandrous

- Start date

Scroll to continue with content

Please attempt your own homework.

We aren't going solve it for you.

If you need help with something, ask a question pertaining to how you can come to a solution.

i already designed the johnson counter but i dont know how to stop counting when its is reached at a particular stateNo different than any other counter. FSM, present-state>next-state, and all that...

What is the next state relative to the present state if you don't want it to advance on a clock?i already designed the johnson counter but i dont know how to stop counting when its is reached at a particular state

You look at the outputs with a decoder. When the decoder says you've reached the terminal state. You turn off the count enable, or you block the clock from allowing the counter to continue. It's a fielders choice. You could also use the decoder to parallel load the final state into the counter for each consecutive clock pulse until a RESET gets you out.

my concept is that i just want the johnson counter till 1111111.so when next state 1111110 comes i fed back it into clocking circuit using a logic circuit such that it preventing clock at this stageYou look at the outputs with a decoder. When the decoder says you've reached the terminal state. You turn off the count enable, or you block the clock from allowing the counter to continue. It's a fielders choice. You could also use the decoder to parallel load the final state into the counter for each consecutive clock pulse until a RESET gets you out.

my concept is that i just want the johnson counter till 1111111.so when next state 1111110 comes i fed back it into clocking circuit using a logic circuit such that it preventing clock at this stageWhat is the next state relative to the present state if you don't want it to advance on a clock?

Gateing a clock on/off is usually problematic. It is much better to design the counter so that the last state just repeats over and over on every subsequent clock.

Begs the question: how do you get the counter out of the last state, and make it start over? Asynchronous reset? Extra input which is acted on upon a clock?

Begs the question: how do you get the counter out of the last state, and make it start over? Asynchronous reset? Extra input which is acted on upon a clock?

Gateing a clock on/off is usually problematic. It is much better to design the counter so that the last state just repeats over and over on every subsequent clock.

Begs the question: how do you get the counter out of the last state, and make it start over? Asynchronous reset? Extra input which is acted on upon a clock?

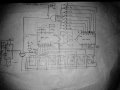

check the circuit i have drawn ..it is for testing a dac ic..the concept is that a dac ic convert digital input to analogue and this analogue is passed to the adc..and the obtained digital output is compared with the input ..when the sequence in input and output is same its clocked the flipflop to count next state and so on..when ever there is a mismatch between input and output the counting is stopes and fail indication led is lightsIf you are using a parallel load to hold the last state you can add a mux to allow the jam transfer of an initial state as well. Then everything is nice and synchronous.

i wish to use johnson counter for chekcing particular inputs

Moderators note: I reduced the colors and size of the image

Attachments

-

589 KB Views: 17

Last edited by a moderator:

| Thread starter | Similar threads | Forum | Replies | Date |

|---|---|---|---|---|

| G | Johnson counter design | Homework Help | 5 | |

| G | Up/Down Johnson Counter | Digital Design | 39 | |

|

|

Design a johnson counter using D-flip flops | Homework Help | 13 | |

| B | johnson counter | Homework Help | 5 | |

| B | 3 bit Johnson counter | Homework Help | 1 |

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin