Hello,

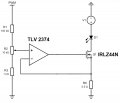

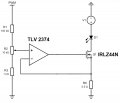

my goal was to design a constant current source for driving a LED array with the use of an input/output rail-to-rail operational amplifier (TLV2374) with 5V single supply. I went for the simplest design I could find, namely a unity gain bufffer, whose output is connected to the gate terminal of a logic level MOSFET (IRLZ44N). Voltage signal that is being fed to the non-inverting input is in the form of a sinusoidal PWM signal with carrier frequency of 44100 kHz and a logic high of 5V. The potentiometer enables changing the current through the LED from 1V to 100mA by the use of a sense resistor of 0.5Ω. A scheme of the circuit is shown below:

Unfortunately, at that time I thought this to be a failproof design and hence did not do more research or detailed simulations. When it came to PCB assemblying and testing, I found the circuit to be very unstable, with significant peaking during transient step response and subsequent oscillations being present.

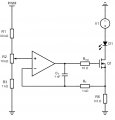

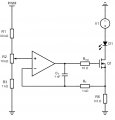

I found this to be due to reduced phase margin, caused by the capacitive loading of the MOSFET, which, according to the datasheet has an input capacitance of 1700pF, while the op-amp can handle capacitive loads of max. 10pF without the need of additional compensation. I then have searched for compensation techniques and went for the circuit depicted below:

If my understanding is correct, the isolation resistor Riso, combined with the feedback capacitor Cf and resistor Rf, forms a bypass for the high frequency signal and therefore prevents phase margin decrease. Furthermore, I simulated the non-compensated and compensated version of the constant current source in LTspice to determine the change in phase margin. The results are shown below:

The compensated circuit shows no peaking or oscillation and has a phase margin of 50°, which is satisfying, however the simulation has been done with a sinusoidal AC signal of amplitude 1V instead with PWM signal. Would it therefore be a better idea to further increase phase margin or is the compensated circuit already good enough for production?

Thank you for your advice!

Edit: Provided LTspice simulation files and model files for op-amp and MOSFET

my goal was to design a constant current source for driving a LED array with the use of an input/output rail-to-rail operational amplifier (TLV2374) with 5V single supply. I went for the simplest design I could find, namely a unity gain bufffer, whose output is connected to the gate terminal of a logic level MOSFET (IRLZ44N). Voltage signal that is being fed to the non-inverting input is in the form of a sinusoidal PWM signal with carrier frequency of 44100 kHz and a logic high of 5V. The potentiometer enables changing the current through the LED from 1V to 100mA by the use of a sense resistor of 0.5Ω. A scheme of the circuit is shown below:

Unfortunately, at that time I thought this to be a failproof design and hence did not do more research or detailed simulations. When it came to PCB assemblying and testing, I found the circuit to be very unstable, with significant peaking during transient step response and subsequent oscillations being present.

I found this to be due to reduced phase margin, caused by the capacitive loading of the MOSFET, which, according to the datasheet has an input capacitance of 1700pF, while the op-amp can handle capacitive loads of max. 10pF without the need of additional compensation. I then have searched for compensation techniques and went for the circuit depicted below:

If my understanding is correct, the isolation resistor Riso, combined with the feedback capacitor Cf and resistor Rf, forms a bypass for the high frequency signal and therefore prevents phase margin decrease. Furthermore, I simulated the non-compensated and compensated version of the constant current source in LTspice to determine the change in phase margin. The results are shown below:

The compensated circuit shows no peaking or oscillation and has a phase margin of 50°, which is satisfying, however the simulation has been done with a sinusoidal AC signal of amplitude 1V instead with PWM signal. Would it therefore be a better idea to further increase phase margin or is the compensated circuit already good enough for production?

Thank you for your advice!

Edit: Provided LTspice simulation files and model files for op-amp and MOSFET

Attachments

-

1.9 KB Views: 0

-

6.4 KB Views: 0

-

2 KB Views: 0

Last edited:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin