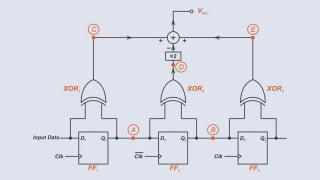

Hi all. I am trying to verify the output for 4 bit SAR logic. So far this is my schematic:

My output plot is showing the expect results of: 1000, 1100, 1110, and 1111 but it doesn't reset after the fourth clock cycle:

These are the values for each component:

My output plot is showing the expect results of: 1000, 1100, 1110, and 1111 but it doesn't reset after the fourth clock cycle:

These are the values for each component:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin