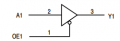

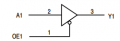

I am having difficulty getting an NXP LPC2134 into bootload mode for ISP using simple mechanical switching. An alternative is to let the RS232 programmer control DTS/RTS to get into that state. NXP gives an interface for that which uses an xx125 (tri-state, non-inverting buffer):

My favorite surplus store in Cleveland (ESI) is effectively closed for the time being. In the NXP design, A1 is grounded. I wonder whether the "high impedance" state of a PIC is sufficiently high to emulate the "open" state for that chip. For example, when OE1 is low, YI would be an output set to low. When OE1 is high, TRIS for the Y1 pin would be set (i.e., input). There would be no WPU. Maximum "open" leakage current for the 125 is 10 uA.

My favorite surplus store in Cleveland (ESI) is effectively closed for the time being. In the NXP design, A1 is grounded. I wonder whether the "high impedance" state of a PIC is sufficiently high to emulate the "open" state for that chip. For example, when OE1 is low, YI would be an output set to low. When OE1 is high, TRIS for the Y1 pin would be set (i.e., input). There would be no WPU. Maximum "open" leakage current for the 125 is 10 uA.

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin