Hello,

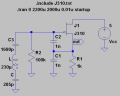

I was trying to build Clapp oscillator with a JFET (J310) as it is shown in the figure.

Capacitor C is variable and goes from 20 pF to 285 pF. I have connected C3 in series to get suitable equivalent capacitance. With the given values I should get frequencies between 800 kHz and 2 MHz. The simulation confirms this.

However, the circuit on the bench does not behaves as in the simulation. With C = 285 pF I get about 800 kHz with about 3.6 Vpp. Once I start to decrease C the output amplitude starts to decrease and at about 1.5 MHz the oscillator stops. Shouldn't the amplitude be approximately constant as it is in the simulation? Why it decreases? Does the transistor gain goes down and why?

I have tried with a breadboard and with a PCB (Manhattan style) and the results are the same.

Best regards,

Mirko

I was trying to build Clapp oscillator with a JFET (J310) as it is shown in the figure.

Capacitor C is variable and goes from 20 pF to 285 pF. I have connected C3 in series to get suitable equivalent capacitance. With the given values I should get frequencies between 800 kHz and 2 MHz. The simulation confirms this.

However, the circuit on the bench does not behaves as in the simulation. With C = 285 pF I get about 800 kHz with about 3.6 Vpp. Once I start to decrease C the output amplitude starts to decrease and at about 1.5 MHz the oscillator stops. Shouldn't the amplitude be approximately constant as it is in the simulation? Why it decreases? Does the transistor gain goes down and why?

I have tried with a breadboard and with a PCB (Manhattan style) and the results are the same.

Best regards,

Mirko

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin