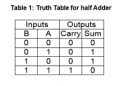

Hey all, the first image attached is a half-adder circuit with the simulation and timings, are the sum & carry delay timings right? If not how do I calculate them correctly? The simulation shows the start and end point (blue and yellow vertical lines) and the T1-T2 is how I calculated it at first.

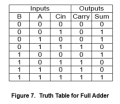

The second image attached is a 3-bit synchronous binary counter with timings in (ns), again I don't think that the timings are right, how would I set up the T1 and T2 lines to find out the period of most significant bit and the clock transition to output delay?

The second image attached is a 3-bit synchronous binary counter with timings in (ns), again I don't think that the timings are right, how would I set up the T1 and T2 lines to find out the period of most significant bit and the clock transition to output delay?

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin