i'm working on an H bridge with TO220 pow mosfets, it's actually a hobby project tought to be published online, after some effort to develop the "control" section with decent success i bumped on a weird and hardly replicable effect on the mosfet's gates, before building anything and wasting components and especially fuses i'd like to know if this effect is a LTSpice "bug" or it's a real word issue

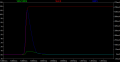

when the upper Pmos closes very rapidly (1 us rise time) and the Nmos gate is held low the Pmos pulls the drain of the Nmos (obvious) but on it's turn the Nmos gate tries to pull high the control circuit with 1A actually succeeding and reaching 2.5V for a brief period, this closes the Nmos when the Pmos closes generating a tremendous current spike trought the two transistors

is it a real issue or i can ignore it and build the thing?

when the upper Pmos closes very rapidly (1 us rise time) and the Nmos gate is held low the Pmos pulls the drain of the Nmos (obvious) but on it's turn the Nmos gate tries to pull high the control circuit with 1A actually succeeding and reaching 2.5V for a brief period, this closes the Nmos when the Pmos closes generating a tremendous current spike trought the two transistors

is it a real issue or i can ignore it and build the thing?