Hello,

Class B push pull amplifiers like the one shown here http://www.allaboutcircuits.com/vol_6/chpt_6/10.html

are explained when it comes to class b push pull amplifiers in the sources I have found.

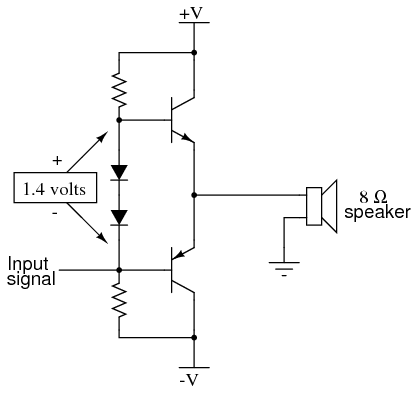

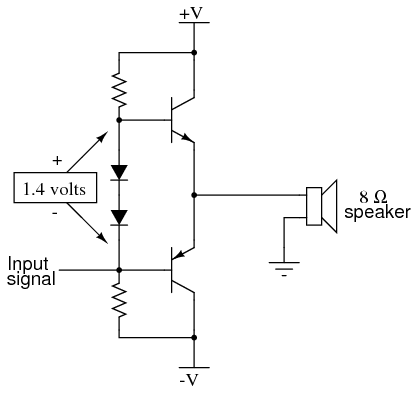

But I have encountered class b push pull like the one shown in the attachment. Afaik it works in the following way. There is 10V with respect to the ground on the output coupling capacitor. As a result each transistor gets 10V between the emitter and the collector and the polarities are correct. When the positive swing of the input comes NPN conducts and the capacitor charges. When the negative swing comes PNP conducts and the capacitor discharges. (So, when the negative swing comes the capacitor becomes the "power supply" of the circuit)

My doubt is: What if the input signal comes like the attached example. The positive swing is much "larger" than the negative one. If the capacitor is charged during the positive swing, say, from 10V to 13V (10V + 3V) with respect to the ground, than it is discharged during the negative swing to 12V (13V - 1V) with respect to the ground, than during the next positive swing it charges to 15V (12V + 3V), and so on. I know the amplifier does not behave the way I just described (I have done a simulation). I know it is a very stupid question but I can't figure out why it behaves the way it does and not the way I described for the life of me

Thanks a lot!

Class B push pull amplifiers like the one shown here http://www.allaboutcircuits.com/vol_6/chpt_6/10.html

are explained when it comes to class b push pull amplifiers in the sources I have found.

But I have encountered class b push pull like the one shown in the attachment. Afaik it works in the following way. There is 10V with respect to the ground on the output coupling capacitor. As a result each transistor gets 10V between the emitter and the collector and the polarities are correct. When the positive swing of the input comes NPN conducts and the capacitor charges. When the negative swing comes PNP conducts and the capacitor discharges. (So, when the negative swing comes the capacitor becomes the "power supply" of the circuit)

My doubt is: What if the input signal comes like the attached example. The positive swing is much "larger" than the negative one. If the capacitor is charged during the positive swing, say, from 10V to 13V (10V + 3V) with respect to the ground, than it is discharged during the negative swing to 12V (13V - 1V) with respect to the ground, than during the next positive swing it charges to 15V (12V + 3V), and so on. I know the amplifier does not behave the way I just described (I have done a simulation). I know it is a very stupid question but I can't figure out why it behaves the way it does and not the way I described for the life of me

Thanks a lot!

Attachments

-

5.7 KB Views: 51

-

6.3 KB Views: 46