Full adder Circuit Proof

- Thread starter testing12

- Start date

Scroll to continue with content

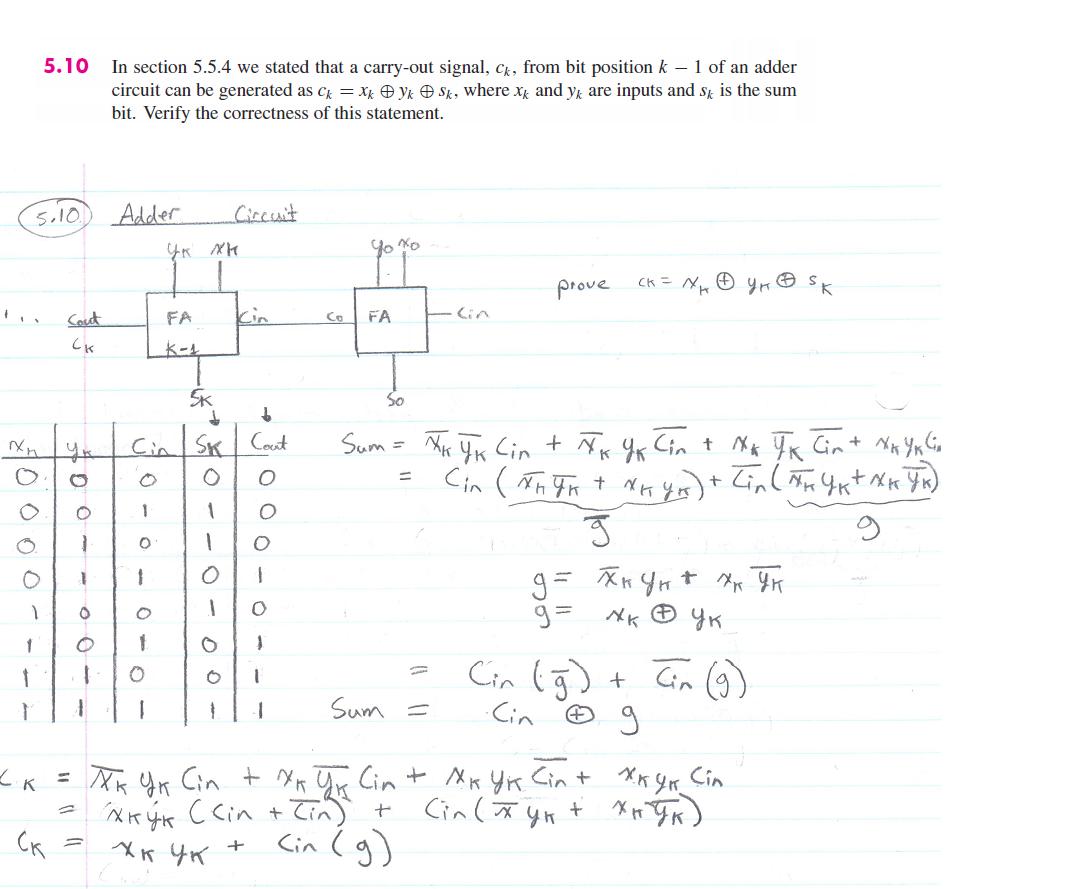

Clarify me this: \(c_k\) is \(c_{in}\) or \(c_{out}\)? If it is \(c_{in}\) I can agree, based only on your truth table. If it is \(c_{out}\) however I can't see how the question can be confirmed.

You can make your proof much easier if you keep in mind that multiple XOR gates will function as an Odd Function (will say if the numbers of ones is odd).

You can make your proof much easier if you keep in mind that multiple XOR gates will function as an Odd Function (will say if the numbers of ones is odd).

This is the relevant portion:

LIBRARY ieee ;

USE ieee.std logic 1164.all ;

USE ieee.std logic signed.all ;

ENTITY adder16 IS

PORT ( X, Y : IN STD LOGIC VECTOR(15 DOWNTO 0) ;

S : OUT STD LOGIC VECTOR(15 DOWNTO 0) ) ;

END adder16 ;

ARCHITECTURE Behavior OF adder16 IS

BEGIN

S < X+Y ;

END Behavior ;

Figure 5.27 VHDL code for a 16-bit adder.

The code in Figure 5.27 does not include carry-in or carry-out signals. Also, it does not provide the arithmetic overflow signal. One way in which these signals can be added is given in Figure 5.28. The 17-bit signal named Sum isdefined in the architecture. The extra bit, Sum(16), is used for the carry-out from bit-position 15 in the adder. The statement used

to assign the sum of X, Y, and the carry-in, Cin, to the Sum signal uses an unusual syntax.

The meaning of the term in parentheses, namely (0& X), is that a 0 is concatenated to the

16-bit signal X to create a 17-bit signal. In VHDL the & operator is called the concatenate

operator. The reader should not confuse this meaning with the more traditional meaning

of & in other hardware description languagesin which it isthe logical AND operator. The

reason that the concatenate operator isneeded in Figure 5.28 isthat VHDL requiresat least

one of the operands of an arithmetic expression to have the same number of bits as the

result. Because Sum isa 17-bit operand, then at least one of X or Y must be modified to

become a 17-bit number.

Another detail to observe from the figure is the statement

S <= Sum(15 DOWNTO 0) ;

This statement assigns the lower 16 bits of Sum to the output sum S. The next statement

assigns the carry-out from the addition, Sum(16), to the carry-out signal, Cout. The expression

for arithmetic overflow was defined in section 5.3.5 as cn−1 ⊕ cn. In our case, cn

corresponds to Sum(16), but there is no direct way of accessing cn−1, which isthe carry-out

from bit-position 14. The reader should verify that the expression X(15)⊕Y(15)⊕Sum(15)

corresponds to cn−1

LIBRARY ieee ;

USE ieee.std logic 1164.all ;

USE ieee.std logic signed.all ;

ENTITY adder16 IS

PORT ( X, Y : IN STD LOGIC VECTOR(15 DOWNTO 0) ;

S : OUT STD LOGIC VECTOR(15 DOWNTO 0) ) ;

END adder16 ;

ARCHITECTURE Behavior OF adder16 IS

BEGIN

S < X+Y ;

END Behavior ;

Figure 5.27 VHDL code for a 16-bit adder.

The code in Figure 5.27 does not include carry-in or carry-out signals. Also, it does not provide the arithmetic overflow signal. One way in which these signals can be added is given in Figure 5.28. The 17-bit signal named Sum isdefined in the architecture. The extra bit, Sum(16), is used for the carry-out from bit-position 15 in the adder. The statement used

to assign the sum of X, Y, and the carry-in, Cin, to the Sum signal uses an unusual syntax.

The meaning of the term in parentheses, namely (0& X), is that a 0 is concatenated to the

16-bit signal X to create a 17-bit signal. In VHDL the & operator is called the concatenate

operator. The reader should not confuse this meaning with the more traditional meaning

of & in other hardware description languagesin which it isthe logical AND operator. The

reason that the concatenate operator isneeded in Figure 5.28 isthat VHDL requiresat least

one of the operands of an arithmetic expression to have the same number of bits as the

result. Because Sum isa 17-bit operand, then at least one of X or Y must be modified to

become a 17-bit number.

Another detail to observe from the figure is the statement

S <= Sum(15 DOWNTO 0) ;

This statement assigns the lower 16 bits of Sum to the output sum S. The next statement

assigns the carry-out from the addition, Sum(16), to the carry-out signal, Cout. The expression

for arithmetic overflow was defined in section 5.3.5 as cn−1 ⊕ cn. In our case, cn

corresponds to Sum(16), but there is no direct way of accessing cn−1, which isthe carry-out

from bit-position 14. The reader should verify that the expression X(15)⊕Y(15)⊕Sum(15)

corresponds to cn−1

Okay, as we said before, you can verify that

\(c_{in,k}=x_k\ XOR\ y_k\ XOR\ s_k\)

by looking at your truth table.

You can either do this visually by noticing that the XOR/odd function is confirmed, or by manipulating the minterms, in order to build the XOR function from scratch.

\(c_{in,k}=x_k\ XOR\ y_k\ XOR\ s_k\)

by looking at your truth table.

You can either do this visually by noticing that the XOR/odd function is confirmed, or by manipulating the minterms, in order to build the XOR function from scratch.

| Thread starter | Similar threads | Forum | Replies | Date |

|---|---|---|---|---|

|

|

Need help with 74ls193 | Digital Design | 12 | |

|

|

Logic circuit projects issue | Homework Help | 69 | |

| R | Designing a logic circuit using a full adder? | Homework Help | 7 | |

|

|

Static CMOS switch-level circuit to for a "¬Cout" full-adder circuit | Homework Help | 0 | |

| I | Half adder/Full adder circuit | Homework Help | 3 |

You May Also Like

-

Semidynamics Provides All-In-One AI IP to Facilitate AI Chip Design

by Jake Hertz

-

Introspect Technology Introduces LPDDR5/LPDDR5X Protocol Analyzer

by Duane Benson

-

AMD Launches Embedded+ Architecture Blending Ryzen and Versal

by Jake Hertz

-

ISSCC 2024: MediaTek Presents Neural Visual-Enhancement Engine for IoT

by Jake Hertz