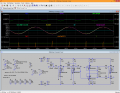

Hello, i am trying to model op amp to boost high impedance (10-100)microVolts to (plusMinus 1volt )...please see attached simulation design, from first stage i have boosted (input delta20uV) to (output (pink wave)about delta49mV). which is at dc level +3.23V.......but am having problem adding the second stage....(blue wave) possitive peak is good to 1.5v but negative peak doesn't look right

.....any suggestions please...or links to resources i could look into...thank you.

.....any suggestions please...or links to resources i could look into...thank you.

.....any suggestions please...or links to resources i could look into...thank you.

.....any suggestions please...or links to resources i could look into...thank you.