Hello,

I have designed a small PCB to use at home. It will be some kind of device for a smart home, the goal is to control the heater automatically through the relays, control the lighting through ZIGBEE and detect if there's someone in bed with a load sensor. This will be a shield to connect to the Attiny817 Xplained Mini. I have attached the schematic of the circuit that I designed. The board will be power supplied by the USB Micro connector. I will solder the components by hand.

I would like someone to indicate improvements over the layout.

1) I am worried about the U1 ADS1231, I couldn't find a layout recommendation. This IC is analog so I don't know if the placement is correct.

2) What do you think about the placement of the capacitors around the U1 and U2?

3) The connector J5 belongs to the ZIGBEE module, 410-201, because it's analog too, should I create a separate ground for it?

4) I still have layer 3 free, I don't know what is the best thing to do with that one.

5) What about the ramification of the 5V on the bottom layer? The traces have 40 mils, it should be more than enough.

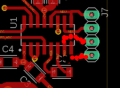

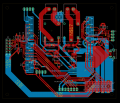

TOP Layer 1 :

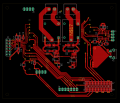

BOTTOM Layer 4 :

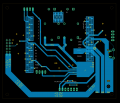

GND Layer 2 :

Thank you in advance.

I have designed a small PCB to use at home. It will be some kind of device for a smart home, the goal is to control the heater automatically through the relays, control the lighting through ZIGBEE and detect if there's someone in bed with a load sensor. This will be a shield to connect to the Attiny817 Xplained Mini. I have attached the schematic of the circuit that I designed. The board will be power supplied by the USB Micro connector. I will solder the components by hand.

I would like someone to indicate improvements over the layout.

1) I am worried about the U1 ADS1231, I couldn't find a layout recommendation. This IC is analog so I don't know if the placement is correct.

2) What do you think about the placement of the capacitors around the U1 and U2?

3) The connector J5 belongs to the ZIGBEE module, 410-201, because it's analog too, should I create a separate ground for it?

4) I still have layer 3 free, I don't know what is the best thing to do with that one.

5) What about the ramification of the 5V on the bottom layer? The traces have 40 mils, it should be more than enough.

TOP Layer 1 :

BOTTOM Layer 4 :

GND Layer 2 :

Thank you in advance.

Last edited: