I've been working with load cells for a long time now, and one of the problems that I have not yet been able to solve to my satisfaction is offset drift. Offset drift is the drift in output voltage over time even when the cell is under no load.

A while back, I found this very interesting circuit that excites the cell using a 400Hz AC signal:

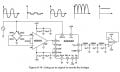

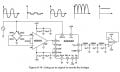

In Figure 6-14, a 400 Hz signal excites the bridge. The signal at the AD8221’s input is an ac voltage. Similarly, the signal at the input of the AD630 is ac; the signal is dc at the end of the low-pass filter following the AD630.

The 400 Hz ac signal is rectified and then averaged; dc errors are converted in an ac signal and removed by the AD630. Ultimately, a precision dc signal is obtained.

The AD8221 is well-suited for this application because its high CMRR over frequency ensures that the signal of interest, which appears as a small difference voltage riding on a large sinusoidal common-mode voltage, is gained and the common-mode signal is rejected. In typical instrumentation amplifiers, CMRR falls off at about 200 Hz. In contrast, the AD8221 continues to reject common-mode signals beyond 10 kHz.

If an ac source is not available, a commutating voltage may be constructed using switches. The AD8221’s high CMRR over frequency rejects high frequency harmonics from a commutating voltage source.

I have several questions regarding this circuit:

A while back, I found this very interesting circuit that excites the cell using a 400Hz AC signal:

Strain Gage Measurement Using An AC Excitation

Strain gage measurements are often plagued by offset drift, 1/f noise, and line noise. One solution is to use an ac signal to excite the bridge, as shown in Figure 6-14. The AD8221 gains the signal and an AD630AR synchronously demodulates the waveform. What results is a dc output proportional to the strain on the bridge. The output signal is devoid of all dc errors associated with the in-amp and the detector, including offset and offset drift.

In Figure 6-14, a 400 Hz signal excites the bridge. The signal at the AD8221’s input is an ac voltage. Similarly, the signal at the input of the AD630 is ac; the signal is dc at the end of the low-pass filter following the AD630.

The 400 Hz ac signal is rectified and then averaged; dc errors are converted in an ac signal and removed by the AD630. Ultimately, a precision dc signal is obtained.

The AD8221 is well-suited for this application because its high CMRR over frequency ensures that the signal of interest, which appears as a small difference voltage riding on a large sinusoidal common-mode voltage, is gained and the common-mode signal is rejected. In typical instrumentation amplifiers, CMRR falls off at about 200 Hz. In contrast, the AD8221 continues to reject common-mode signals beyond 10 kHz.

If an ac source is not available, a commutating voltage may be constructed using switches. The AD8221’s high CMRR over frequency rejects high frequency harmonics from a commutating voltage source.

I have several questions regarding this circuit:

- Would the AC signal have to be precise and with zero-drift too? (I'm assuming that's a no)

- Is there any other demodulator chip that could be used? The AD630 costs more than 20 bucks!

- How precise would the ±15V sources have to be? Would simple 7815 and 7915 regulators do?

- Is there a different circuit you may suggest that I should try, so as to accomplish my zero-drift goal?