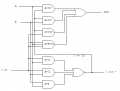

Other posts were old or difficult to read. Here is an example of a full adder not using Exclusive-OR gates.

You can find more info on data sheets for 7480 or ITT9304.

Approach:

What input conditions are required to make the Sum output a high?

What input conditions are required to generate a Carry out?

So why does the 7480 and 9304 have so many more inputs? These devices can add, subtract, create parity checking, convert grey to binary ...

Check out the data sheets for these devices. Examples of use are usually shown.